- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

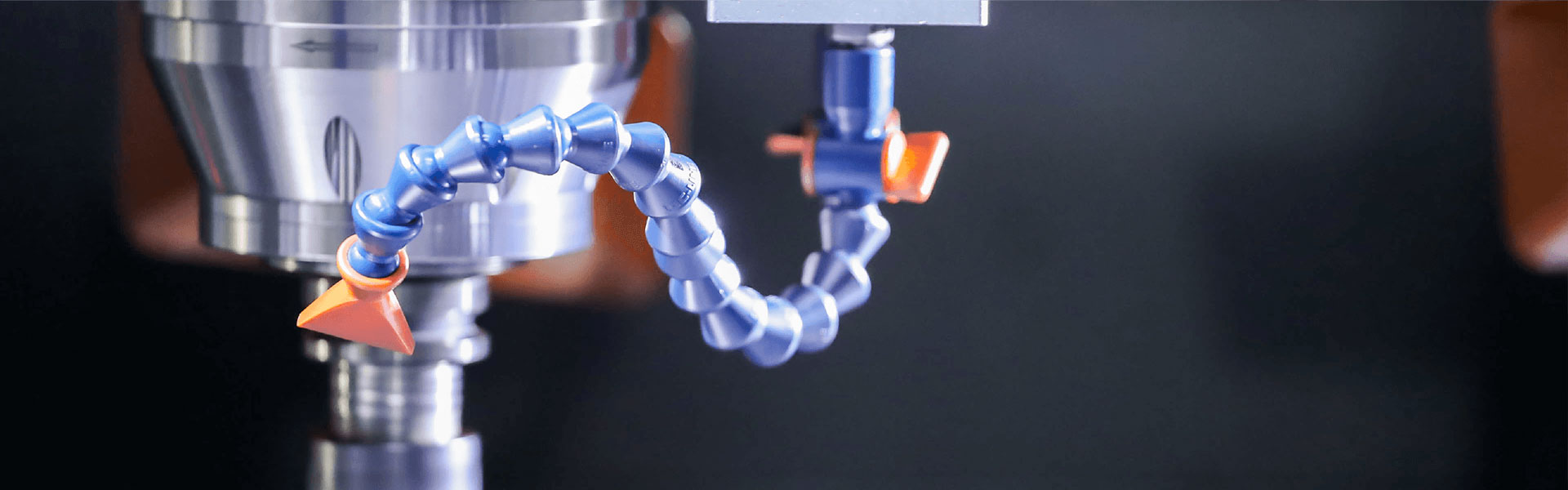

Kakšen je postopek epitaksija SiC?

Na področju visoke napetosti, zlasti za visokonapetostne naprave nad 20.000 V, jeSiC epitaksialnotehnologija se še vedno sooča s številnimi izzivi. Ena glavnih težav je doseganje visoke enakomernosti, debeline in koncentracije dopinga v epitaksialni plasti. Za izdelavo takšnih visokonapetostnih naprav je potrebna 200 um debela epitaksialna rezina iz silicijevega karbida z odlično enakomernostjo in koncentracijo.

Pri izdelavi debelih SiC filmov za visokonapetostne naprave pa lahko pride do številnih napak, predvsem trikotnih. Te napake lahko negativno vplivajo na pripravo visokotokovnih naprav. Zlasti, ko se čipi z veliko površino uporabljajo za ustvarjanje visokih tokov, se življenjska doba manjšinskih nosilcev (kot so elektroni ali luknje) znatno skrajša. To zmanjšanje življenjske dobe nosilca je lahko problematično za doseganje želenega toka naprej v bipolarnih napravah, ki se običajno uporabljajo v visokonapetostnih aplikacijah. Za pridobitev želenega toka naprej v teh napravah mora biti življenjska doba manjšinskega nosilca vsaj 5 mikrosekund ali več. Vendar pa je tipičen parameter življenjske dobe manjšinskega nosilca zaSiC epitaksialnorezin je približno 1 do 2 mikrosekundi.

Zato, čeprav jeSiC epitaksialnoproces dosegel zrelost in lahko izpolnjuje zahteve nizko- in srednjenapetostnih aplikacij, so potrebni nadaljnji napredki in tehnične obdelave za premagovanje izzivov v visokonapetostnih aplikacijah. Izboljšave enakomernosti debeline in koncentracije dopinga, zmanjšanje trikotnih napak in podaljšanje življenjske dobe manjšinskih nosilcev so področja, ki zahtevajo pozornost in razvoj, da bi omogočili uspešno implementacijo SiC epitaksialne tehnologije v visokonapetostnih napravah.